Внимание

Мы работаем в штатном режиме. Наши склады готовы поставлять оборудование клиентам из Российской Федерации несмотря на санкционные запреты ЕС и США. Оборудование в РФ ввозится легально благодаря новому законодательству с параллельным импортом. Звоните и уточняйте! Информация актуальна на 27.04.26В связи с участившимися случаями недобросовестной конкуренции обращаем ваше внимание, что мы не передаем персональные данные третьим лицам

Поиск по сайту

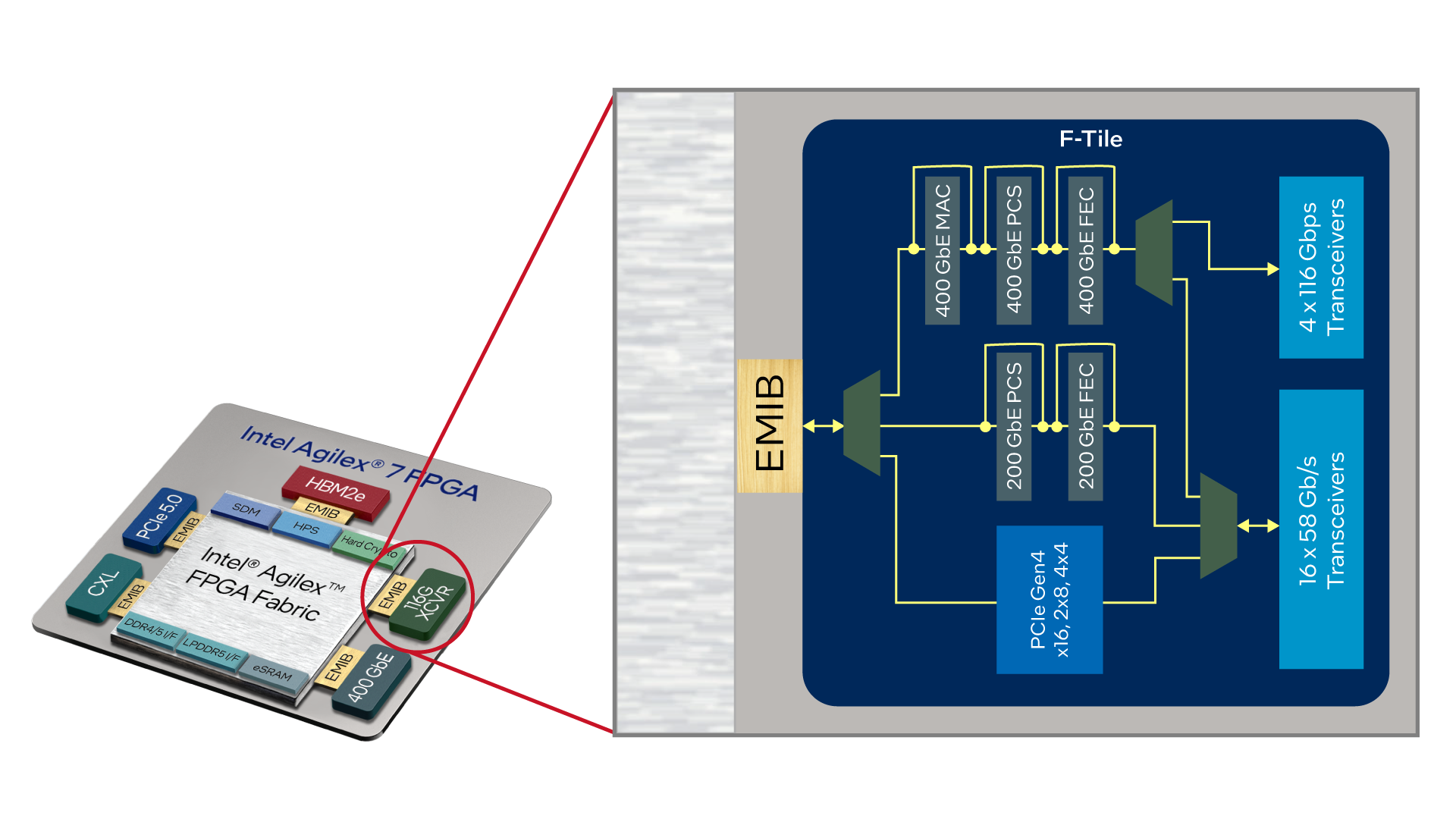

Intel представила FPGA Agilex 7 с высокоскоростными трансиверами F-Tile

FPGA остаются популярными как гибкие решения, пригодные для реализации широкого круга задач по ускорению обработки данных. Однако с ростом пропускной способности современных сетей растут соответствующие требования и к FPGA. Ответом на вызовы в этом сегменте стал выпуск новой серии ПЛИС Intel Agilex 7 с самыми быстрыми в мире FPGA трансиверами F-Tile.

F-Tile — двухрежимный последовательный интерфейс, предлагающий схемы модуляции PAM4 и NRZ. Он может работать на скоростях до 116 Гбит/с. Также предлагается реализация Ethernet вплоть до 400GbE. Каждый тайл такого типа может содержать до четырёх высокоскоростных каналов FHT с поддержкой PAM4 и до 16 менее скоростных каналов FGT, ограниченных 58 Гбит/с в режиме PAM4 и 32 Гбит/с в режиме NRZ. Количество F-тайлов в составе Agilex 7 зависит от конкретной модели чипа.

Наличие столь высокопроизводительных трансиверов в составе Agilex 7 делает новые ПЛИС Intel отлично подходящими для поддержки высокоскоростных сетей (в качестве DPU), в том числе беспроводных, или для ИИ-ускорителей. Производительностью Agilex 7 не обделены — для старшей серии M говорится о 38 Тфлопс, правда, в режиме FP16.

Базируются новые ПЛИС на уже не слишком новом 10-нм техпроцессе Intel 7 Enhanced SuperFin, и в старшей серии M могут предоставить в распоряжение разработчику 3,85 млн логических элементов, 12300 блоков DSP и 370 Мбайт быстрой интегрированной памяти, а также до 32 Гбайт памяти в HBM2e-сборках. Также в составе присутствует квартет ядер Arm Cortex-A53. Agilex 7 поддерживают интерфейс PCI Express 5.0 и CXL 1.1 (посредством R-Tile).

Таким образом, программируемые матрицы Intel Agilex 7 благодаря сочетанию быстрых трансиверов и интерфейсов HBM2e и LPDDR5 найдут применение в любых сценариях, где требуется обработка существенных массивов данных: в периферийных системах первичной обработки данных, решениях искусственного интеллекта, при развёртывании сетей 5G и даже в сфере HPC.

Нужно больше информации?

Обратитесь к специалистам компании KVANTECH